# Improvement on Leakage Current Performance of Semiconductor IC Packages by Eliminating ESD Events

Frederick Ray I. Gomez

Back-End Manufacturing & Technology, STMicroelectronics, Inc.

9 Mountain Drive, Light Industry & Science Park II, Brgy. La Mesa, Calamba City, Laguna, Philippines 4027

\*\*Email: frederick-ray.gomez [AT] st.com\*\*

ABSTRACT— The technical paper discusses the reduction of high leakage current failures of semiconductor IC (integrated circuit) packages by eliminating the ESD (electrostatic discharge) events during assembly process and ensuring the appropriate machine grounding and ESD controls. It is imperative to reduce or ideally eliminate the leakage current failures of the device to ensure the product quality, especially as the market becomes more challenging and demanding. After implementation of the corrective and improvement actions, high leakage current occurrence was reduced from baseline of 5784 ppm to 1567 ppm, better than the six sigma goal of 4715 ppm.

Keywords—Semiconductor packages, IC, leakage current, ESD

## 1. INTRODUCTION

With any semiconductor manufacturing company's absolute aim to sustain on being the benchmark of manufacturing excellence, there is still a requirement to deliver excellent quality products through innovative, fast, and cost effective solutions. Semiconductor industries offer broad range of IC packages for different kinds of applications, ranging from automotive, consumer electronics, industrial, Internet of Things (IoT), etc., and one of which is the Quad-Flat No-leads Multi-Row (QFN-mr) leadframe device being used as motor controllers on hard disk drives. The device (hereinafter referred to as Device X) is designed with Advanced Bipolar-CMOS-DMOS (BCD8) technology and packaged on QFN-mr platform utilizing a tapeless leadframe technology. As the die technology scales down, circuit metallization also becomes smaller. In turn, the device or package becomes more sensitive and susceptible to electrostatic discharge (ESD) damage. Presence of static charges, improper grounding, speed of material separation, and triboelectric charging (or simply tribocharging) could cause ESD damage to ESD-sensitive device. Fundamentals of ESD and ESD damage are discussed in-depth in the ESD Association references [1]. As the product time-to-market becomes more demanding and challenging, there is a great drive to address package-related issues at the soonest as possible.

## 1.1 Package Defect on Focus

Parametric Parts Average Testing (PPAT) on leakage current response was employed at the Final Test to filter or screen-out units that are outliers (above 5-sigma) based on a reference distribution. Figure 1 shows the outliers on 1 lot of Device X. The reference distribution is obtained on the response of the first 50 units tested at the Final Test.

Figure 1: Leakage current PPAT response, showing the outliers

Note that it is imperative to reduce the leakage current failures to ensure the product quality. If the leaky unit/device is functioning, that leaky connection will eventually degrade and become open-circuit and eventually disabling the functionality of the device.

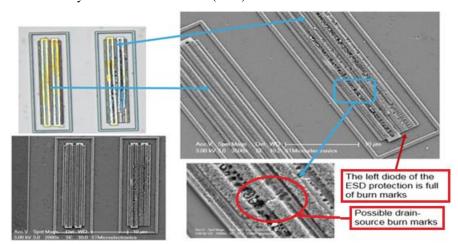

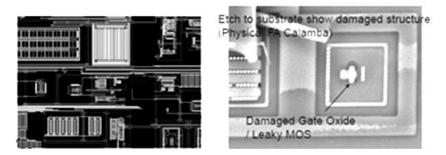

Most of the rejections do not manifest any abnormality after Failure Analysis (FA) since the leakage current readings are still within the defined specification limits. However, the units are considered failing since they are outliers from the PPAT testing. For units above the specification limit, FA showed burnt metallization as shown in Figure 2. This defect manifestation could be caused by an electrical overstress (EOS) or ESD issue.

Figure 2: Defect manifestation possibly caused by ESD or EOS

## 1.2 Defect Ppm Baseline and Six Sigma Goal

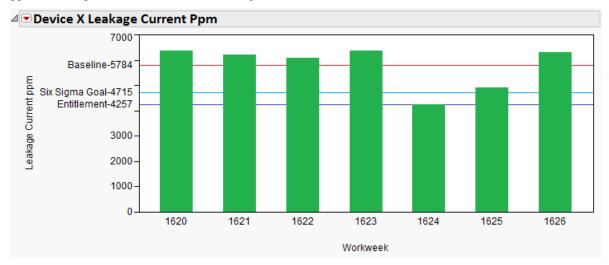

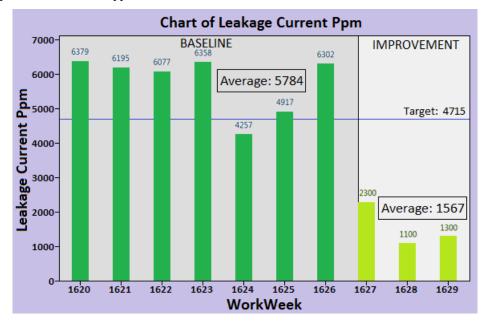

Baseline is initially computed to be at 5784 ppm. With entitlement of 4257 ppm, the calculated Six Sigma Goal is at 4715 ppm (70% improvement), as illustrated in Figure 3.

Figure 3: Baseline and six sigma goal

The lots processed on workweek 1625 to 1626 showed that most of the defectives lie on 0.57% and the long term sigma (current process capability) was calculated to be at 2.5309. Figure 4 shows the Device X current process capability.

Figure 4: Current process capability

## 1.3 Objective Statement

From the calculations shown earlier, the objective is to ultimately reduce the leakage current rejections from 5784 average ppm to 4715 ppm or even lower. As previously emphasized, it is of high importance to reduce or eliminate the occurrence of leakage current failures to ensure the product quality. Leaky units will eventually degrade and affect the performance the device.

#### 2. LITERATURE REVIEW

From literature studies, known causes of high leakage current rejections and damaged metallization related to assembly manufacturing are summarized as:

- Electrostatic damage to sensitive devices [1]

- Metallization damage brought by plasma charging [2]

- Tribocharging effects due to high waterjet parameters [3] [4] [5]

- High moisture content after waterjet process [3] [4] [6]

- High wafer saw transfer arm speeds and high water resistivity [5] [7]

- Trapped charges on high resistivity mold compounds [8]

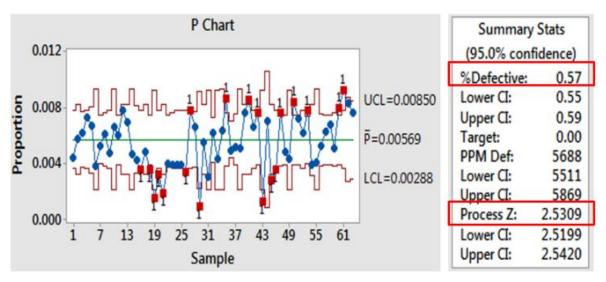

Electrostatic discharge damage to units can be explained by three models [1] [6] given in Figure 5.

Figure 5: ESD models

A study [2] showed that plasma process with high cleaning parameters resulted to damage gate oxide, as illustrated in Figure 6.

Figure 6: Damage gate oxide with plasma process

Triboelectric charging (or tribocharging) effects brought by high waterjet deflash parameters were also studied [3] [4] [6]. Lower waterjet pressure and temperature resulted to lower supply current failures. Some of the failures were also recovered after subjecting the units to baking which removed the package moisture content.

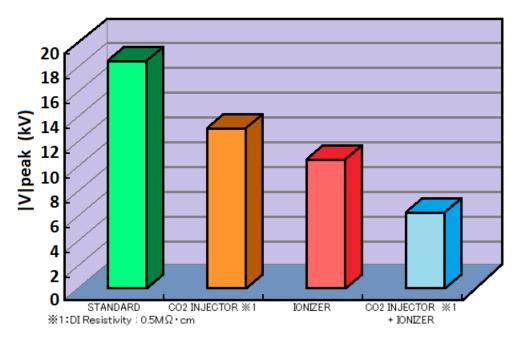

Wafer saw process could also contribute to the device's susceptibility to ESD damage. Processing without carbon dioxide (CO<sub>2</sub>) bubbler and ionizer showed higher discharge voltage at around 18kV [5] as compared to a saw process with the required accessories, as shown in Figure 7. Additional study showed that faster transport speed of 300m/s during wafer transfer at wafer saw station resulted to higher discharge voltage than that of a slower 5mm/s transport speed [5] [7].

Figure 7: Discharge voltage at wafer saw process [5]

Previous study also showed that leakage current was experienced on some molding compounds due to thermally induce trapped charge failure mechanism [8].

#### 3. METHODOLOGY

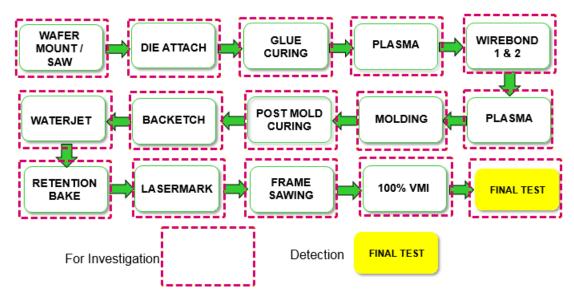

A macro map was checked to determine the project scope. All process stations will be investigated since all of these steps could induce ESD damage to the units (possible failure mechanism).

Figure 8: Process macro map

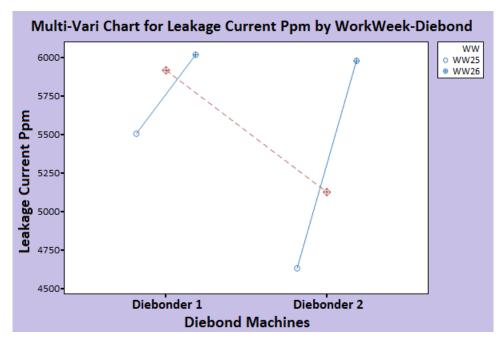

Multi-Vari analysis was carried out to determine which process step or equipment is contributing to higher rejections. It was found out that one diebond machine is causing higher leakage current rejections, as shown in Figure 9. Investigation showed that there were ESD Events (> 1 kV) on Diebonder 1. The machine was then subjected to health check and the ESD events were zeroed out by grounding the machine floating parts.

Figure 9: Multi-vari analysis on diebond machines

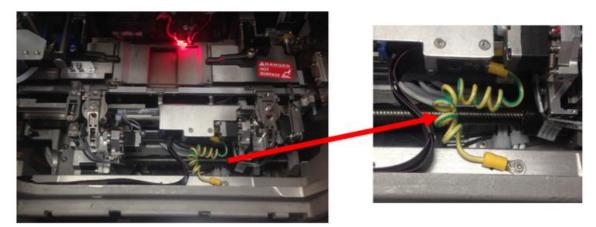

With the findings, ESD events were checked in all process steps and equipment. Machine grounding from all process steps were checked and the ones failing were corrected. Figure 10 illustrates wirebond workholder's grounding connected to its machine body.

Figure 10: Wirebond workholder machine grounding

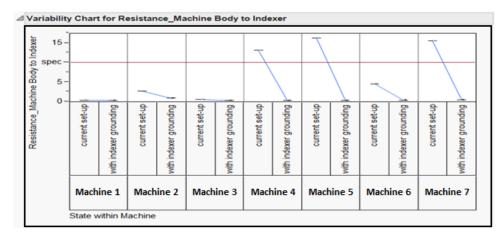

Connecting the workholder to the machine body reduced the resistance level to less than  $10\Omega$ . Figure 11 shows the resistance readings after grounding the workholder (current set-up vs with workholder indexer grounding).

Figure 11: Resistance reading, before and after machine grounding

#### 4. RESULTS AND ANALYSIS

After implementation of the corrective and improvement actions, leakage current occurrence greatly reduced from a baseline of 5784 ppm to average of 1567 ppm last workweek 1627-29, as shown in Figure 12. This is significantly better than the target performance at 4715 ppm.

Figure 12: Leakage current ppm improvement

Specifications such as FMEA (Failure Mode and Effects Analysis), Control Plan, and Work Instructions were updated based on the findings and the corrective and improvement actions done. It is of high importance to make sure that proper grounding is installed in all machines. This is to ensure that any static charges and/or any charge build-up on the machine will be dissipated or discharged to ground through the metal components and the machine body.

## 5. CONCLUSIONS AND RECOMMENDATIONS

Leakage current performance was significantly improved by eliminating ESD events through grounding of floating machine parts, maintaining the acceptable resistance value according to the specifications, and sustaining ESD controls. The leakage current occurrence decreased from a baseline of 5784 ppm to 1567 ppm after implementation of the improvement and corrective actions. This was achieved taking into account the motivation to deliver quality products given the challenging market cycle time.

Continuous improvement is important for sustaining the quality excellence of any product and of the assembly plant. One opportunity for further improvement is the optimization of the  $CO_2$  bubbler and explore its resistivity settings so as to reduce the  $CO_2$  consumption, at the waterjet deflash station.

## 6. ACKNOWLEDGMENT

The author would like to acknowledge the great effort and contribution of Tito Mangaoang Jr., who led the leakage current task force team. T. Mangaoang is also a co-author of many technical papers [4] [6] and a co-inventor of a US patent application. The author would like to extend the appreciation to the leakage current task force team and to the Management Team for the utmost support.

#### 7. REFERENCES

- [1] ESD Association, "Fundamentals of ESD, device sensitivity and testing", Rome, New York, USA, 2011.

- [2] E. Padilla and T. Lacuesta, "Plasma optimization in addressing test leakage fails for BCD wafer technology", Presented at the 25th ASEMEP Technical Symposium, June 2015.

- [3] A. Sumagpang Jr., F.A. Llana, and E. Padilla, "Practical, cost efficient, and systematic approach in resolving supply current failures during unit testing of QFN-mr BiCMOS device", Presented at the 26th ASEMEP Technical Symposium, Manila, Philippines, June 2016.

- [4] F.R. Gomez and T. Mangaoang Jr., "Elimination of ESD events and optimizing waterjet deflash process for reduction of leakage current failures on QFN-mr leadframe devices", Journal of Electrical Engineering, David Publishing Co., vol. 6, no. 4, pp. 238-243, July 2018.

- [5] DISCO Engineering R&D Division, "Wafer ESD in dicing saws and the effect of the countermeasures", Presented at the DISCO Technical Review, February 2016.

- [6] T. Mangaoang Jr., F.R. Gomez, and D. Burguillos Jr., "Reduction of leakage current failures on QFN-mr devices through DMAIC methodology", Presented at the 27th ASEMEP Technical Symposium, Manila, Philippines, June 2017.

- [7] M. Sato, "Static electricity handbook", The Institute of Electrostatics Japan, Ohmsha, Ltd.

- [8] R.D. Mosbarger, and D.J. Hickey, "The effects of materials and post-mold profiles on plastic encapsulated circuits", In Proceedings of 1994 IEEE International Reliability Physics Symposium, San Jose, California, USA, April 1994.